ニュース

電力抑えてAI処理するシリコン光回路を従来比1/17に小型化、KDDI総研と早大

2023年5月1日 06:00

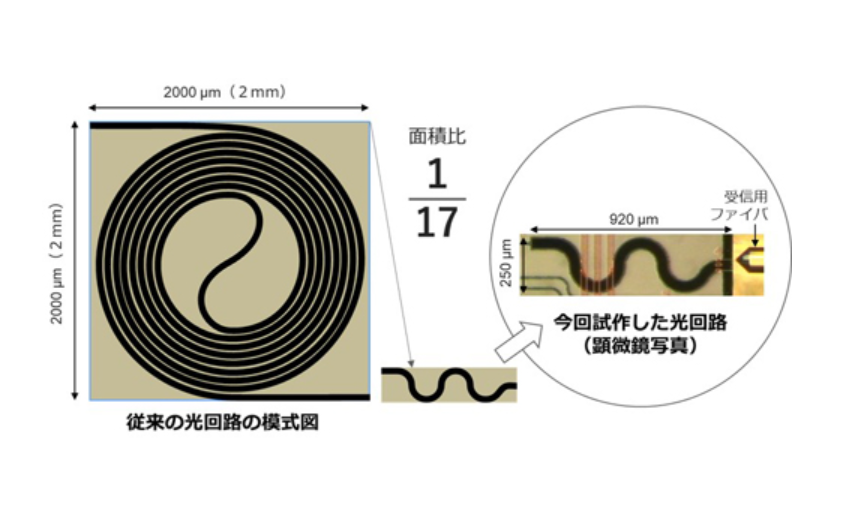

KDDI総合研究所と早稲田大学は、AIの低消費電力化と高速化を目指し、従来比約1/17という面積の光AIアクセラレーター用シリコン光回路を試作し、時系列データの予測に成功した。

両者によれば、注目されるジェネレーティブAIなど最先端のAIは、莫大なコンピューターリソースが必要となる。そのぶん、消費電力量や処理の高速化が課題。一般的には、AIとされる処理は、電子回路上で動作しているが、光AIアクセラレーターは一部の演算を光回路に置き換えるもので、「消費電力の削減に有効で、さらに学習や推論の高速化が可能」として研究開発が盛り上がっている分野という。そのなかでも、シリコン上に形成する光回路は、電子回路や他の光素子と集積化がしやすく、小型化できると期待されている。

今回は、シリコン上に0.25mm×0.92mmというサイズの光回路を試作。これまで採用されてきた光回路向けの構造のうち、渦を巻くような構造と比べ、導路幅を2倍に拡張。蛇行状にして長さを調整して、「短い導波路長でゆっくりと進む光波(高次モード)」を多数発生させた。さらに、信号を高速化したことで、機械学習(リザバーコンピューティング)に必要な、現在の情報と過去の情報を混ぜ合わせるということに成功した。

なおこの成果は、米国サンノゼで開催される光エレクトロニクス関連の総合的な国際学術会議である「CLEO2023」で採択され、現地時間の5月8日に発表される。

今後は、光AIアクセラレーターの実用化に向けて光回路の構造探索や規模拡大を進め、GPUベースのAIアクセラレーターよりも消費電力は1/10に抑え、なおかつ高速に動作する光AIチップの基盤技術の確立を目指す。